降低静态功耗的方法

1、 结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。

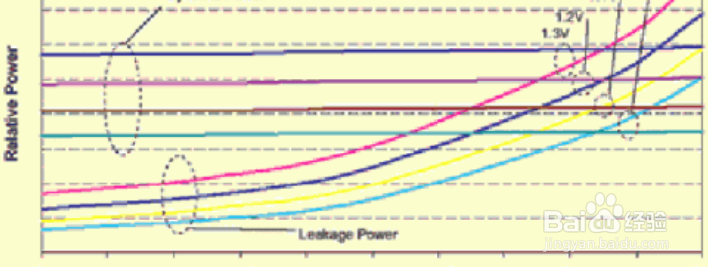

2、 功耗的三个主要来源是启动、待机和动态功耗。器件上电时产生的相关电流即是启动电流;待机功耗又称作静态功耗,是电源开启但I/O上没有开关活动时器件的功耗;动态功耗是指器件正常工作时的功耗。

3、启动电流因器件而异。例如,基于SRAM的FPGA具有高启动电流,因为这类器件刚上电时是没有配置的,而需要从外部存储芯片下载数据来配置它们的可编程资源,如路由连接和查找表。相反地,反熔丝FPGA不需要上电配置,因而没有高启动电流。

4、 像启动电流一样,待机功耗主要依赖于器件的电子特性。由于SRAMFPGA互连中SRAM单元的数量相当大,它们甚至在待机时也要消耗数百毫安电流。反熔丝FPGA具有金属到金属互连,不需要额外的晶体管来保持互连,因而也就不会产生额外的功耗。

5、状态机编码。大量的逻辑资源是由实现的有限状态机的类型来定义的。One-hlt状态机编码创建每个状态的一个触发器的状态机,与Gray和二进制状态机,较少利用one-hot状态机可以获得功效更好的设计。一些综合器软件能自动对状态机进行编码,但最有效的方法是直接在HDL代码中定义状态值。

6、保护赋值。赋值保护的关键在于:若最终的输出不需要更新,则阻止输入信号向下传播到其它逻辑块。对输入信号的赋值保护可确保仅在适当时改变输出值,从而将不必要的输出开关减至最少。